# M68HC05 Applications Guide

# M68HC05 Microcontroller

**Applications Guide**

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function, or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

Motorola and the Motorola logo are registered trademarks of Motorola, Inc.

Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

### **Revision History**

This table summarizes differences between this revision and the previous revision of this applications guide.

| Previous<br>Revision | 2.0                               |

|----------------------|-----------------------------------|

| Current<br>Revision  | 3.0                               |

| Date                 | 06/96                             |

| Changes              | Format and organizational changes |

| Location             | Throughout                        |

MOTOROLA 5

# **Revision History**

M68HC05 Microcontroller Applications Guide

6 MOTOROLA

# **List of Sections**

| General Description         | 21  |

|-----------------------------|-----|

| Microcontroller Operation   | 31  |

| MC68HC705C8 Functional Data | 77  |

| Applications                | 197 |

| Instruction Set Details     | 245 |

| Review Questions            | 315 |

# List of Sections

### **General Description**

| Contents                                     | 21 |

|----------------------------------------------|----|

| Introduction                                 |    |

| Definitions                                  |    |

| Background                                   |    |

| Computer Systems Description                 |    |

| Microcontroller Applications Overview        |    |

| Project Description                          |    |

|                                              |    |

| Microcontroller Operation                    |    |

| Contents                                     | 31 |

| Introduction                                 |    |

| Number Systems                               | 34 |

| Computer Codes                               | 36 |

| Computer Memory                              | 39 |

| Computer Architecture                        | 39 |

| CPU Registers                                | 41 |

| Memory Uses                                  | 43 |

| Memory Maps                                  | 45 |

| Timing                                       | 47 |

| Programming                                  | 48 |

| Flowchart                                    | 49 |

| Mnemonic Source Code                         | 50 |

| Software Delay Program                       | 52 |

| Assembler Listing                            | 54 |

| CPU View of a Program                        | 58 |

| CPU Operation                                | 60 |

| Detailed Operation of CPU Instructions       | 60 |

| Store Accumulator (Direct Addressing Mode)   | 61 |

| Load Accumulator (Immediate Addressing Mode) | 62 |

| Conditional Branch                           | 62 |

| Subroutine Calls and Returns                 | 64 |

| Playing Computer                             |    |

|                                              |    |

M68HC05 Microcontroller Applications Guide — Rev. 3.0

| On-Chip Peripherals                   | 73 |

|---------------------------------------|----|

| Serial Communications Interface (SCI) |    |

| Serial Peripheral Interface (SPI)     |    |

| 16-Bit Timer System                   |    |

| Memory Peripherals                    | 76 |

| Other On-Chip Peripherals             | 76 |

| MC68HC705C8 Functional Data           |    |

|                                       | 77 |

| Contents                              |    |

| MCU Description                       |    |

| Hardware Features                     |    |

| Software Features                     |    |

| General Description                   |    |

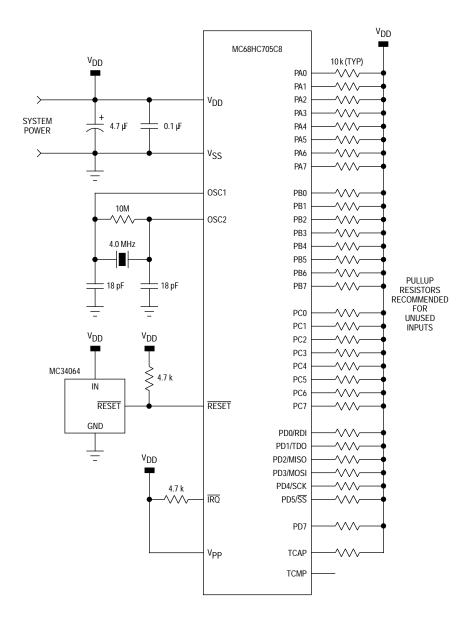

| Pins and Connections                  |    |

| Pin Functions                         |    |

| V <sub>DD</sub> and V <sub>SS</sub>   |    |

| V <sub>PP</sub>                       |    |

| IRQ (Maskable Interrupt Request)      |    |

| RESET                                 |    |

| TCAP                                  |    |

| TCMP                                  |    |

| OSC1 and OSC2                         |    |

| PA7–PA0                               |    |

| PB7–PB0                               |    |

| PC7-PC0                               |    |

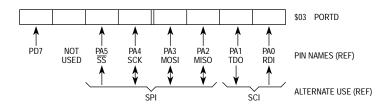

| PD5–PD0 and PD7                       |    |

| Typical Basic Connections             |    |

| On-Chip Memory                        |    |

| Memory Types                          |    |

| Memory Map                            |    |

| Central Processor Unit                |    |

| Registers                             | 94 |

| Accumulator                           | 95 |

| Index Register                        | 95 |

| Condition Code Register               |    |

| Program Counter                       | 98 |

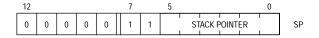

| Stack Pointer                         | 98 |

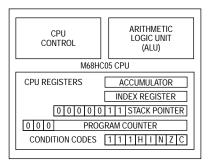

| Arithmetic/Logic Unit (ALU)           |    |

${\sf M68HC05~Microcontroller~Applications~Guide-Rev.~3.0}$

| CPU Control                                          | 99  |

|------------------------------------------------------|-----|

| Resets                                               | 99  |

| Power-On RESET                                       | 99  |

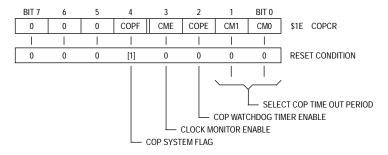

| Computer Operating Properly (COP)                    |     |

| Watchdog Timer RESET                                 | 101 |

| Clock Monitor RESET                                  |     |

| Addressing Modes                                     | 104 |

| Inherent Addressing Mode                             |     |

| Immediate Addressing Mode                            |     |

| Extended Addressing Mode                             |     |

| Direct Addressing Mode                               |     |

| Indexed Addressing Modes                             |     |

| Indexed, No Offset                                   |     |

| Indexed, 8-Bit Offset                                | 115 |

| Indexed, 16-Bit Offset                               | 117 |

| Relative Addressing Mode                             |     |

| Bit Test and Branch Instructions                     |     |

| Instructions Organized by Type                       |     |

| Instruction Set Summary                              |     |

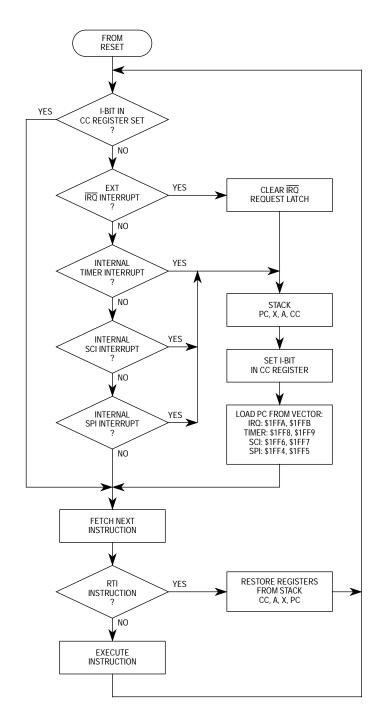

| Interrupts                                           | 134 |

| Software Interrupt (SWI)                             |     |

| External Interrupt                                   | 137 |

| Timer Interrupt                                      | 137 |

| Serial Communications Interface (SCI) Interrupt      | 138 |

| Serial Peripheral Interface (SPI Interrupt           | 138 |

| Microcontroller Input/Output                         | 139 |

| Parallel I/O                                         | 139 |

| Serial I/O                                           |     |

| Serial Communications Interface (SCI)                |     |

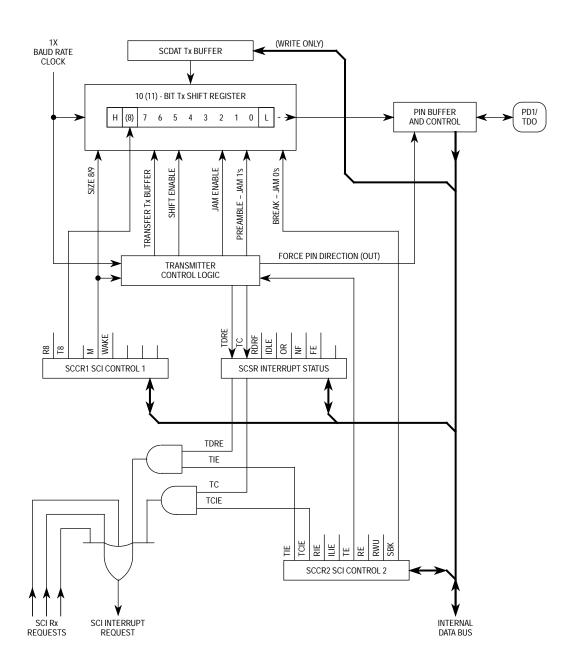

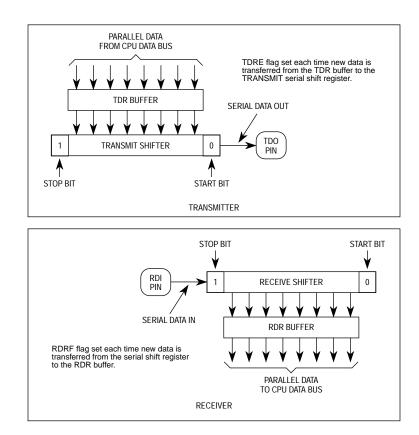

| SCI Transmitter                                      | 144 |

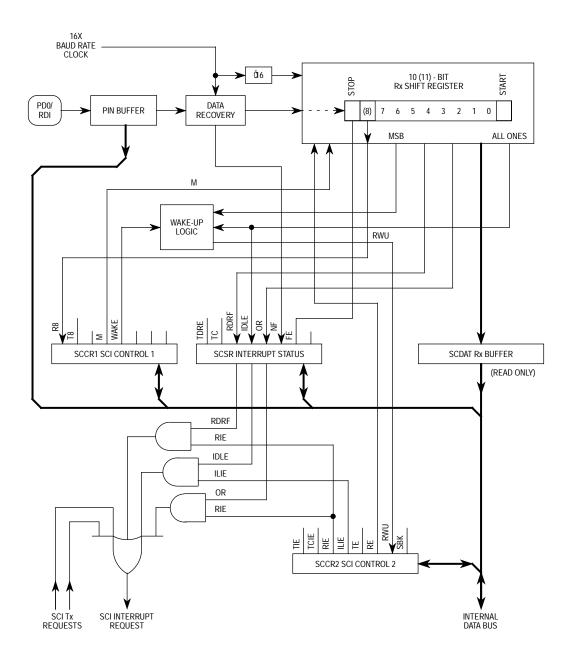

| SCI Receiver                                         |     |

| Registers                                            |     |

| Baud Rate Register (BAUD)                            |     |

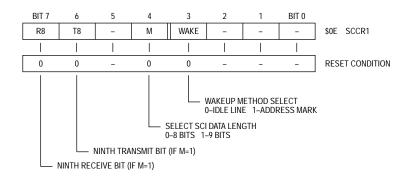

| Serial Communications Control Register One (SCCR1)   | 151 |

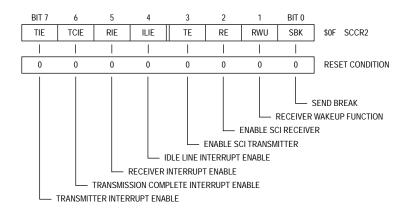

| Serial Communications Control Register Two (SCCR2) . | 152 |

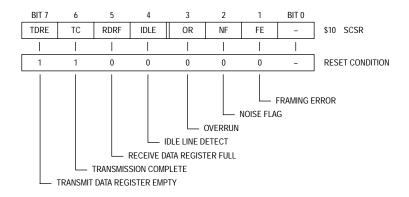

| Serial Communications STATUS Register (SCSR)         | 153 |

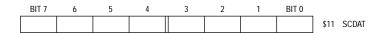

| Serial Communications Data Register (SCDAT)          | 154 |

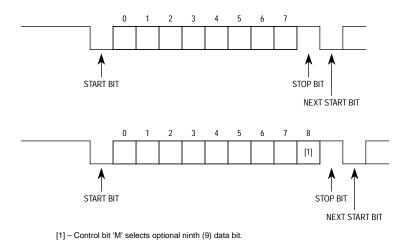

| Data Formats                                         | 155 |

| Hardware Procedures                                  | 155 |

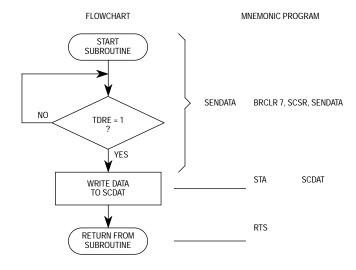

| Software Procedures                                  | 156 |

| Initialization Procedure                      | 156 |

|-----------------------------------------------|-----|

| Normal Transmit Operation                     | 157 |

| Normal Receive Operation                      | 157 |

| SCI Application Example                       | 158 |

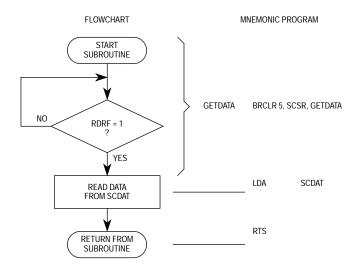

| Synchronous Serial Peripheral Interface (SPI) |     |

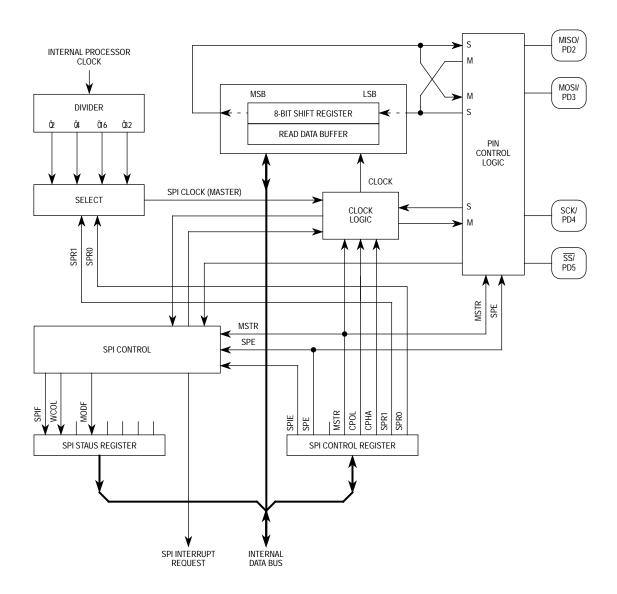

| Data Movement                                 |     |

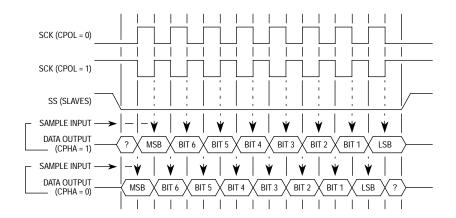

| Functional Description                        | 164 |

| Pin Descriptions                              | 164 |

| Serial Data Pins (MISO, MOSI)                 | 164 |

| Serial Clock (SCK)                            | 165 |

| Slave Select (SS)                             | 165 |

| Registers                                     | 166 |

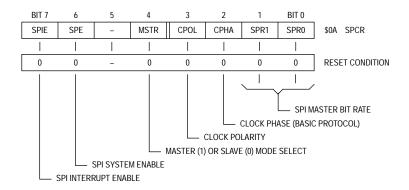

| Serial Peripheral Control Register (SPCR)     | 166 |

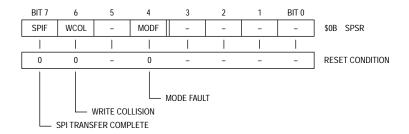

| Serial Peripheral Status Register (SPSR)      | 168 |

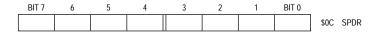

| Serial Peripheral Data I/O Register (SPDR)    |     |

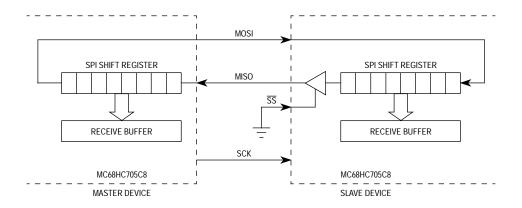

| SPI Application Example                       |     |

| Programmable Timer                            |     |

| Functional Description                        | 176 |

| Timer Counter and Alternate Counter Registers |     |

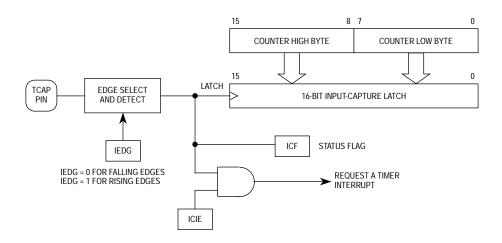

| Input-Capture Concept                         | 179 |

| Input-Capture Operation                       | 180 |

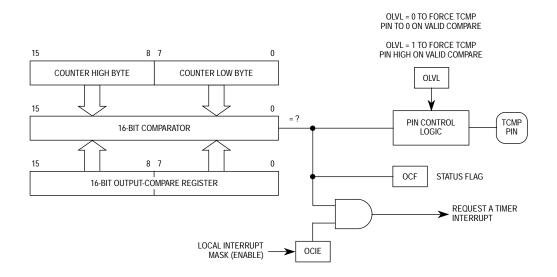

| Output-Compare Concept                        | 182 |

| Output-Compare Operation                      |     |

| Timer Control Register (TCR)                  | 185 |

| Timer Status Register (TSR)                   |     |

| Timer Application Example                     |     |

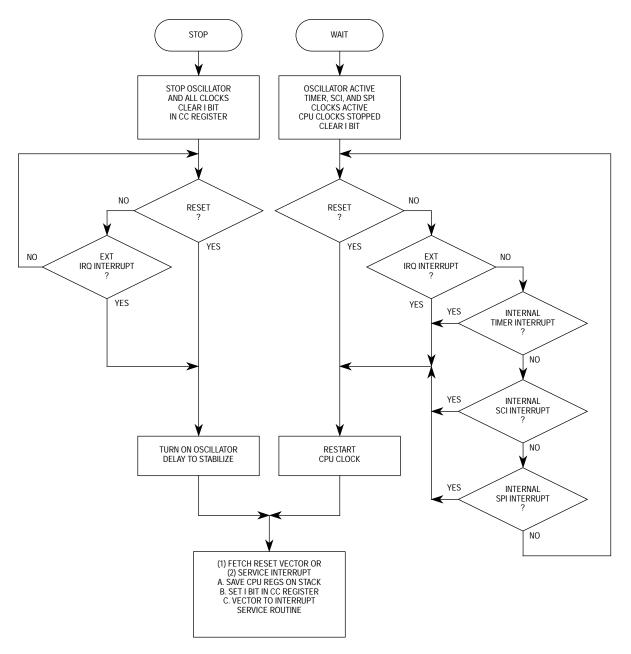

| STOP/WAIT Instruction Effects                 |     |

| Low Power-Consumption Modes                   |     |

| Effects on On-Chip Peripherals                |     |

| Timer Action During STOP Mode                 |     |

| SCI Action During STOP Mode                   |     |

| SPI Action During STOP Mode                   |     |

| Wait Mode Effects                             |     |

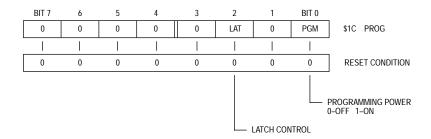

| OTPROM/EPROM Programming                      | 192 |

| Erasing                                       |     |

| Programming                                   |     |

| Program Register                              |     |

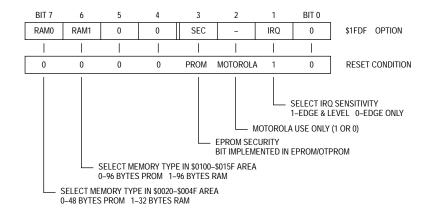

| Option Register                               | 194 |

# **Applications**

| Contents                                                      | .197 |

|---------------------------------------------------------------|------|

| Introduction                                                  | .197 |

| Hardware Development Methods                                  | .199 |

| Software Development Methods                                  |      |

| Freeware                                                      |      |

| Third-Party Software                                          |      |

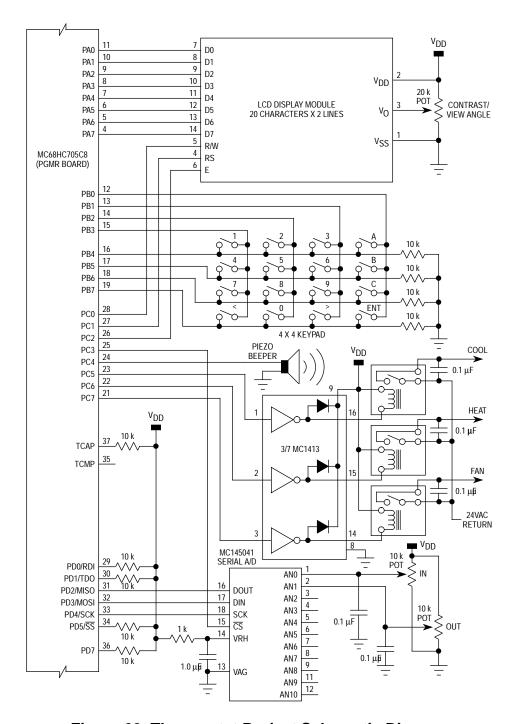

| Thermostat Project Details                                    |      |

| Hardware Details                                              |      |

| Project Programming                                           |      |

| 1 Toject i Togramming                                         | .210 |

| Instruction Set Details                                       |      |

| Contents                                                      | .245 |

| Introduction                                                  | .247 |

| M68HC05 Instruction Set                                       | .249 |

| ADC — Add with Carry                                          | 250  |

| ADD — Add without Carry                                       |      |

| AND — Logical AND                                             |      |

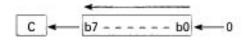

| ASL — Arithmetic Shift Left                                   | 253  |

| ASR — Arithmetic Shift Right                                  | 254  |

| BCC — Branch if Carry Clear                                   | 255  |

| BCLR n — Clear Bit in Memory                                  |      |

| BCS — Branch if Carry Set                                     |      |

| BEQ — Branch if Equal                                         |      |

| BHCC — Branch if Half Carry Clear                             |      |

| BHCS — Branch if Half Carry Set                               |      |

| BHI — Branch if Higher                                        |      |

| BHS — Branch if Higher or Same                                |      |

| BIH — Branch if Interrupt Pin is High                         |      |

| BIL — Branch if Interrupt Pin is Low                          |      |

| BIT — Bit Test Memory with Accumulator                        |      |

| BLO — Branch if Lower                                         |      |

| BLS — Branch if Lower or Same                                 |      |

| BMC — Branch if Interrupt Mask is Clear BMI — Branch if Minus |      |

| BMS — Branch if Interrupt Mask is Set                         |      |

| BNE — Branch if Not Equal                                     |      |

| BPL — Branch if Plus                                          |      |

| BRA — Branch Always                                           |      |

| BRCLR <i>n</i> — Branch if Bit n is Clear                     |      |

| BRN — Branch Never                                            |      |

| BRSET <i>n</i> — Branch if Bit n is Set                       |      |

|                                                               |      |

| BSET <i>n</i> — Set Bit in Memory            | 277 |

|----------------------------------------------|-----|

| BSR — Branch to Subroutine                   | 278 |

| CLC — Clear Carry Bit                        | 279 |

| CLI — Clear Interrupt Mask Bit               | 280 |

| CLR — Clear                                  |     |

| CMP — Compare Accumulator with Memory        | 282 |

| COM — Complement                             |     |

| CPX — Compare Index Register with Memory     | 284 |

| DEC — Decrement                              |     |

| EOR — Exclusive-OR Memory with Accumulator   | 286 |

| INC — Increment                              |     |

| JMP — Jump                                   | 288 |

| JSR — Jump to Subroutine                     | 289 |

| LDA — Load Accumulator from Memory           | 290 |

| LDX — Load Index Register from Memory        | 291 |

| LSL — Logical Shift Left                     |     |

| LSR — Logical Shift Right                    | 293 |

| MUL — Multiply Unsigned                      |     |

| NEG — Negate                                 |     |

| NOP — No Operation                           |     |

| ORA — Inclusive-OR                           |     |

| ROL — Rotate Left thru Carry                 |     |

| ROR — Rotate Right thru Carry                |     |

| RSP — Reset Stack Pointer                    |     |

| RTI — Return from Interrupt                  |     |

| RTS — Return from Subroutine                 |     |

| SBC — Subtract with Carry                    |     |

| SEC — Set Carry Bit                          |     |

| SEI — Set Interrupt Mask Bit                 |     |

| STA — Store Accumulator in Memory            |     |

| STOP — Enable IRQ, Stop Oscillator           |     |

| STX — Store Index Register X in Memory       |     |

| SUB — Subtract                               |     |

| SWI — Software Interrupt                     |     |

| TAX — Transfer Accumulator to Index Register |     |

| TST — Test for Negative or Zero              | 312 |

| TXA — Transfer Index Register to Accumulator |     |

| WAIT — Enable Interrupt, Stop Processor      | 314 |

| Review Questions                             |     |

| Contents                                     | 315 |

| Introduction                                 |     |

| Review Questions                             |     |

| Review Questions, Answers, and Explanations  |     |

| Treview Questions, Answers, and Explanations | J30 |

# **List of Figures**

| Figure | Title                                       | Page |

|--------|---------------------------------------------|------|

| 1      | A Typical Computer System                   | 24   |

| 2      | A Temperature Control Flowchart             | 26   |

| 3      | Thermostat Project Block Diagram            | 28   |

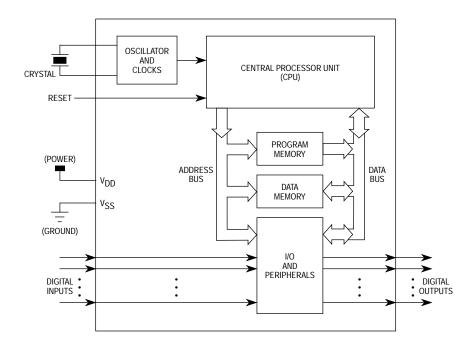

| 4      | MCU Expanded Block Diagram                  | 33   |

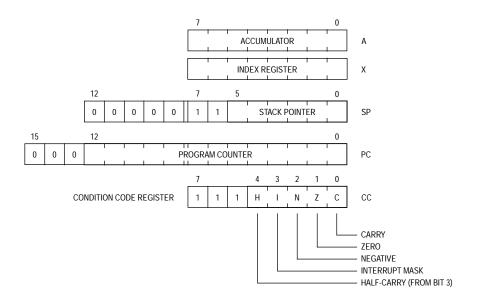

| 5      | M68HC05 CPU Registers                       | 41   |

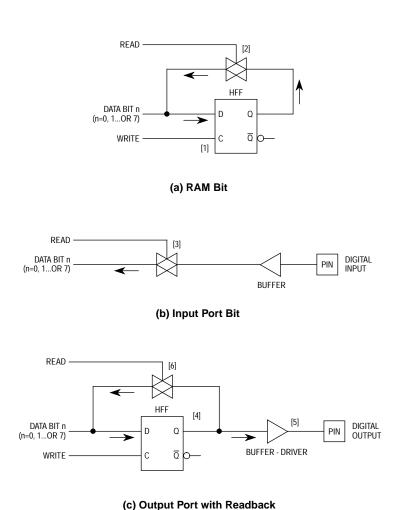

| 6      | Memory and I/O Circuitry                    | 44   |

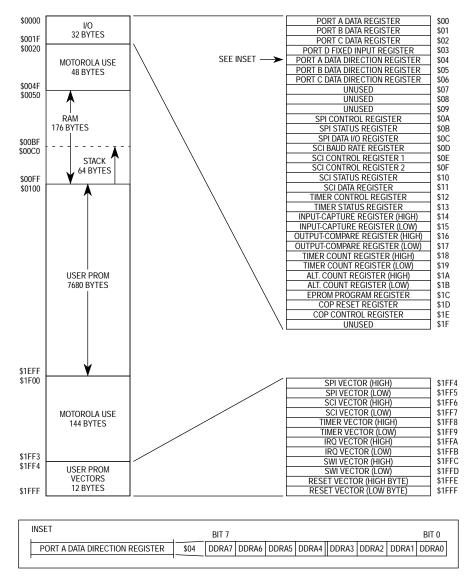

| 7      | Typical Memory Map                          | 45   |

| 8      | Example Flowchart                           | 49   |

| 9      | Flowchart and Mnemonics                     | 51   |

| 10     | Delay Routine Flowchart and Mnemonics       | 52   |

| 11     | Assembler Listing                           | 55   |

| 12     | Explanation of Assembler Listing            | 56   |

| 13     | Memory Map of Example Program               | 59   |

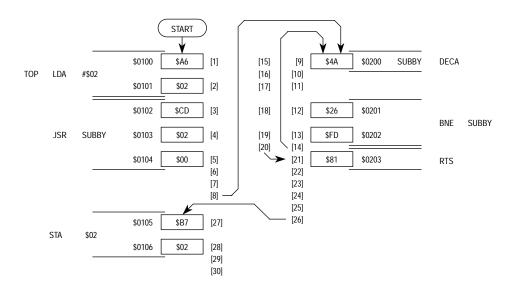

| 14     | Subroutine Call Sequence                    | 65   |

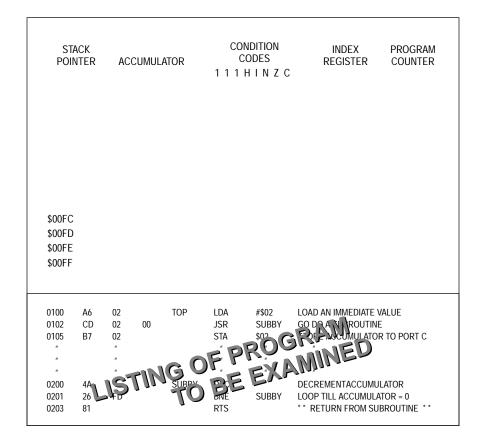

| 15     | Playing Computer Worksheet                  | 69   |

| 16     | Completed Worksheet                         | 70   |

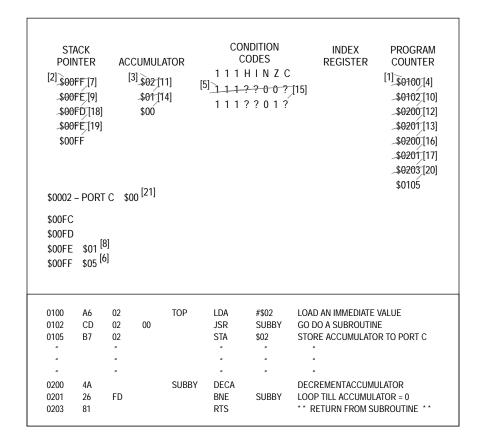

| 17     | MC68HC705C8 Microcontroller Block Diagram   | 83   |

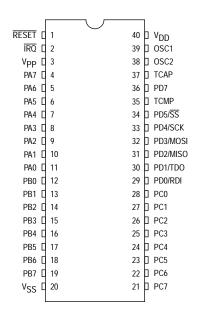

| 18     | 40-Pin Dual-In-Line Package Pin Assignments | 85   |

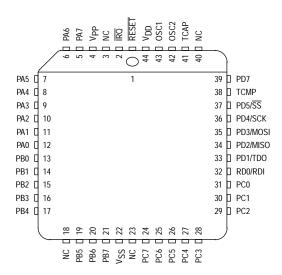

| 19     | 44-Lead PLCC Package Pin Assignments        | 86   |

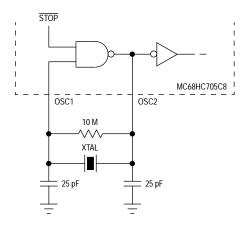

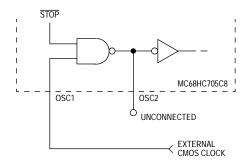

| 20     | Oscillator Connections                      | 87   |

| 21     | Typical Basic Connections                   | 89   |

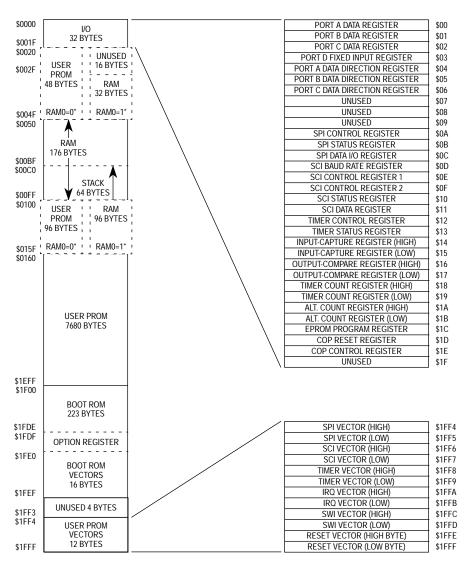

| 22     | MC68HC705C8 Memory Map                      | 92   |

| 23     | M68HC05 CPU Block Diagram                   | 93   |

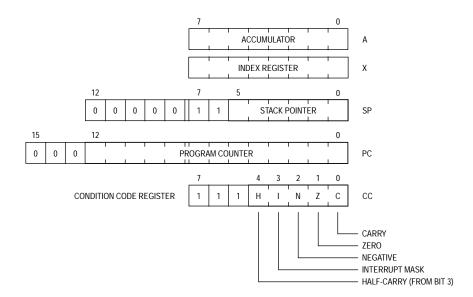

| 24     | Programming Model                           | 94   |

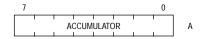

| 25     | Accumulator (A)                             | 95   |

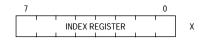

| 26     | Index Register (X)                          | 95   |

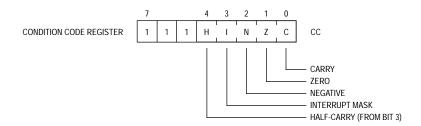

| 27     | Condition Code Register (CCR)               | 96   |

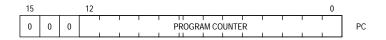

| 28     | Program Counter (PC)                        | 98   |

| 29     | Stack Pointer (SP)                          | 98   |

| 30     | Hardware Interrupt Flowchart                | 136  |

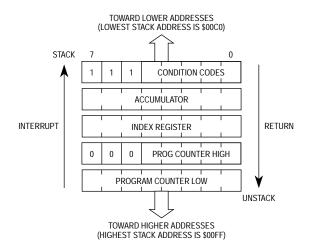

| 31     | Interrupt Stacking Order                    | 137  |

| Figure | Title                                      | Page |

|--------|--------------------------------------------|------|

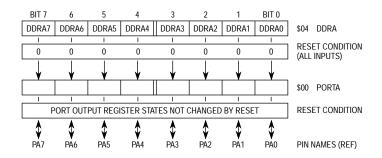

| 32     | Port A and Data Direction A Registers      | 139  |

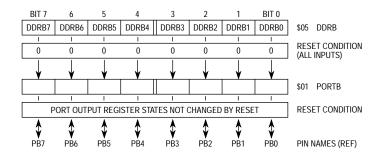

| 33     | Port B and Data Direction B Registers      | 140  |

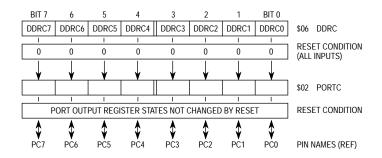

| 34     | Port C and Data Direction C Registers      | 140  |

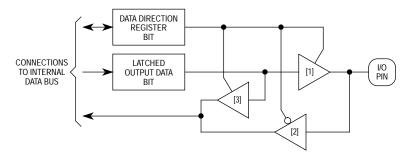

| 35     | Parallel Port I/O Circuitry                | 141  |

| 36     | Port D Fixed Input Port                    | 142  |

| 37     | SCI Transmitter Block Diagram              | 145  |

| 38     | SCI Receiver Block Diagram                 | 147  |

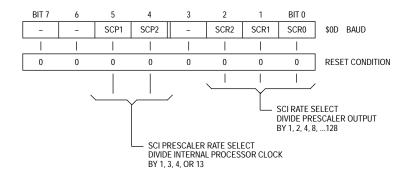

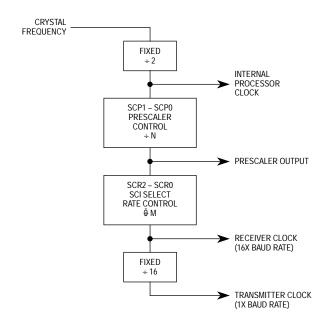

| 39     | Baud Rate Register                         | 149  |

| 40     | Rate Generator Division                    | 149  |

| 41     | Serial Communications Control Register One | 151  |

| 42     | Serial Communications Control Register Two | 152  |

| 43     | Serial Communications Status Register      | 153  |

| 44     | Serial Communications Data Register        | 154  |

| 45     | Double Buffering                           | 154  |

| 46     | Data Formats                               | 155  |

| 47     | SCI Normal Transmit Operation Flowchart    | 157  |

| 48     | SCI Normal Receive Operation Flowchart     |      |

| 49     | SCII Application Example Program           |      |

| 50     | SPI Block Diagram                          | 162  |

| 51     | Shift Register Operation                   |      |

| 52     | Data/Clock Timing Diagram                  |      |

| 53     | Serial Peripheral Control Register         |      |

| 54     | Serial Peripheral Status Register          |      |

| 55     | Serial Peripheral Data I/O Register        |      |

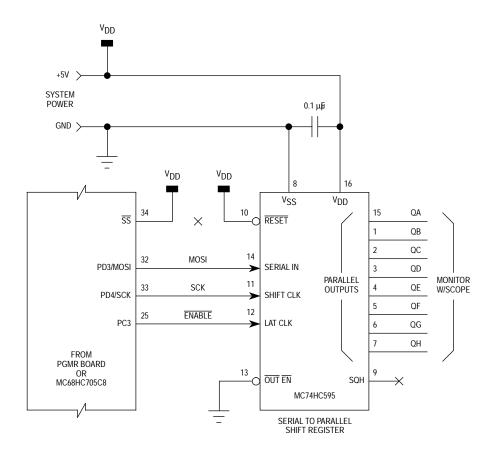

| 56     | SPI Application Example Diagram            |      |

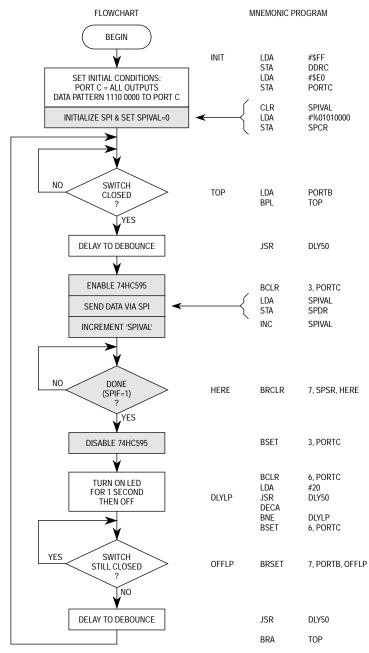

| 57     | SPI Application Example Flowchart          |      |

| 58     | SPI Application Example Program            |      |

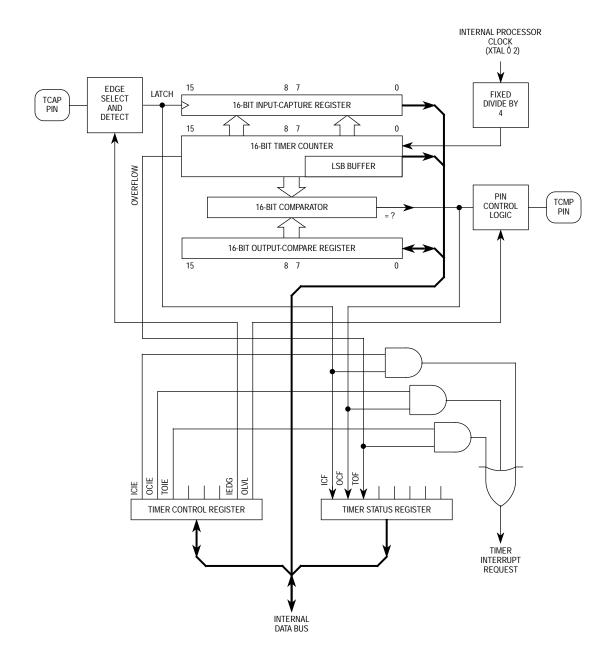

| 59     | Programmable Timer Block Diagram           |      |

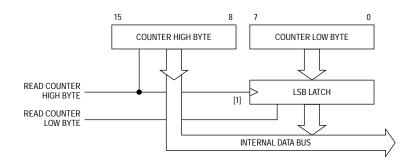

| 60     | 16-Bit Counter Reads                       |      |

| 61     | Input-Capture Operation                    |      |

| 62     | Output-Compare Operation                   |      |

| 63     | Timer Control Register                     |      |

| 64     | Timer Status Register                      |      |

| 65     | Timer Application Example Program          |      |

| 66     | STOP/WAIT Flowchart                        |      |

| 67     | Program Register                           |      |

| 68     | Option Register                            | 194  |

| Figure    | Title                                 | Page |

|-----------|---------------------------------------|------|

| 69        | Thermostat Project Schematic Diagram  | 208  |

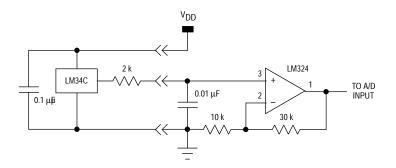

| 70        | Precision Temperature Sensing Circuit | 209  |

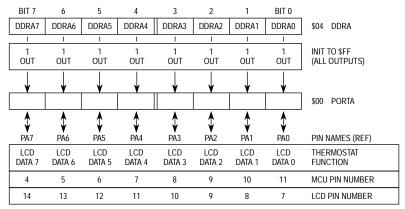

| 71        | Port A Summary                        | 211  |

| 72        | Port B Summary                        | 211  |

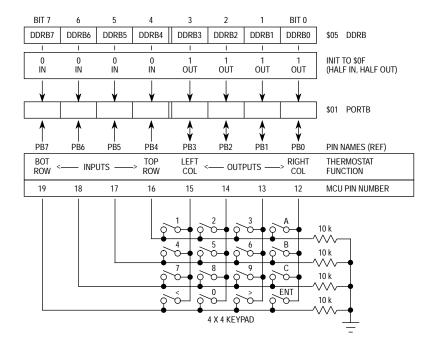

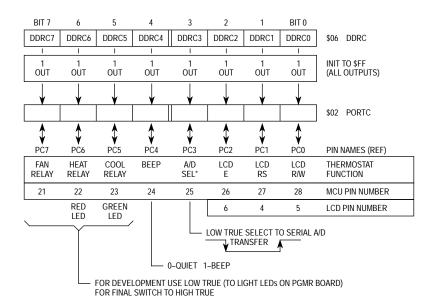

| 73        | Port C Summary                        | 212  |

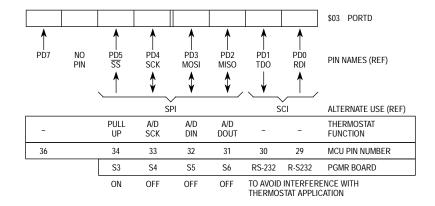

| 74        | Port D Summary                        | 212  |

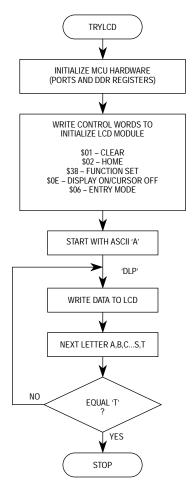

| <b>75</b> | Display Checkout Flowchart            | 214  |

| <b>76</b> | Display Checkout Program Listing      | 216  |

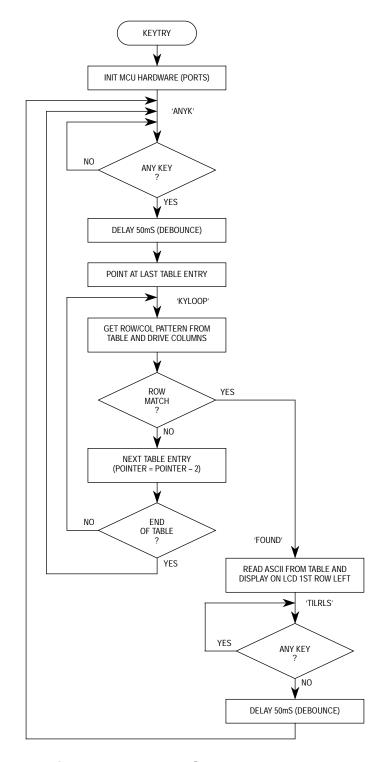

| 77        | Keypad Checkout Flowchart             | 219  |

| 78        | Keypad Checkout Program Listing       | 220  |

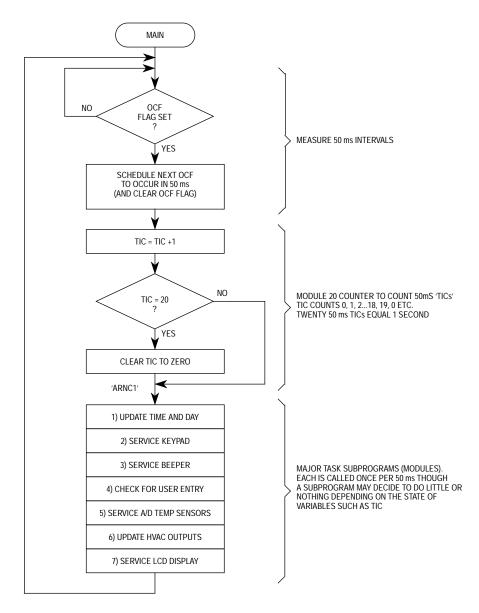

| 79        | Main Program Flowchart                | 222  |

# **List of Tables**

| Table | Title                                       | Page |

|-------|---------------------------------------------|------|

| 1     | Decimal, Binary and Hexadecimal Equivalents | 35   |

| 2     | COP Timeout Period versus CM1 and CM0       | 102  |

| 3     | Register/Memory Instructions                | 122  |

| 4     | Read/Modify-Write Instructions              | 123  |

| 5     | Branch Instructions                         | 124  |

| 6     | Control Instructions                        | 125  |

| 7     | Instruction Set Summary                     | 127  |

| 8     | M68HC05 Instruction Set Opcode Map          | 133  |

| 9     | Vector Address for Interrupts and Reset     | 135  |

| 10    | I/O Pin Functions                           | 141  |

| 11    | Prescaler Baud Rate Frequency Output        | 150  |

| 12    | Transmit Baud Rate Output                   | 151  |

| 13    | ASCII-Hexadecimal Code Conversion           | 159  |

| 14    | Thermostat Project Parts List               | 210  |

# List of Tables

# **General Description**

#### Contents

| Introduction                          | 21 |

|---------------------------------------|----|

| Definitions                           | 22 |

| Background                            | 23 |

| Computer Systems Description          | 24 |

| Microcontroller Applications Overview | 26 |

| Project Description                   |    |

#### Introduction

Welcome to the world of microcontrollers!

In this applications guide, we will develop a project using a Motorola MC68HC705C8 microcontroller unit (MCU) in a familiar application — a home thermostat. The MC68HC705C8 is a member of the M68HC05 Family of MCUs. The project will demonstrate only a few of the many possible microcontroller functions that you can use.

This guide assumes that you have no knowledge of microcontrollers and no MCU applications experience.

**General Description** begins with definitions, gives background information, and describes computer systems. An overview of microcontroller applications is also presented and an application project is discussed.

**Microcontroller Operation** describes in detail how microcontrollers operate.

### General Description

MC68HC705C8 Functional Data contains functional data for the Motorola MC68HC705C8 MCU. This section gives you specific information needed to use this MCU in an application. More information can be found in slightly different form in BR594/D, the MC68HC705C8 Technical Summary, which is available separately.

**Applications** shows you how to develop applications and gives you the thermostat project details.

**Instruction Set Details** provides a detailed description of each instruction in the MC68HC05 instruction set.

**Review Questions** contains review questions, answers, and explanations.

#### **Definitions**

The heart of a computer is the central processor unit (CPU). A microprocessor is a CPU on a single chip.

A computer system is a CPU plus peripherals such as input/output (I/0) devices, memory, a program, and a timing reference.

A microcontroller is a very small product that contains many of the functions found in any computer system. A microcontroller uses a microprocessor (as its CPU) as well as memory and peripherals on the same chip.

A microcontroller (MCU) is packaged as a single chip that can be programmed by the user with a series of instructions loaded into its memory.

#### **Background**

Before MCUs, controllers were hard-wired electronic devices whose operation was determined by the circuits and wires contained within them.

The operation of an MCU-based controller is determined primarily by its program instead of its components and wires. Any function that can be implemented using hard-wired digital integrated circuits (ICs) can also be implemented and performed by an MCU.

As the size and complexity of the devices increase, MCUs become attractive for two reasons:

- 1. The hard-wired approach requires adding ICs to perform more complex tasks; whereas, MCUs require only a longer program.

- Microcontrollers are more versatile. Any change in a hard-wired system usually involves replacing ICs and rerouting wires. Most modifications to an MCU system are made simply by changing the program.

MCUs are very useful where many decisions or calculations are required. It is easier to use the computational power of a computer than to use discrete logic.

Microcontrollers are now being used to replace existing designs because they are far simpler to use than conventional IC logic. Since the MCU approach is programmable, many additional features are possible at little or no added cost. Programmability makes possible multiple use of a common piece of hardware since only the control program needs to be changed.

### **Computer Systems Description**

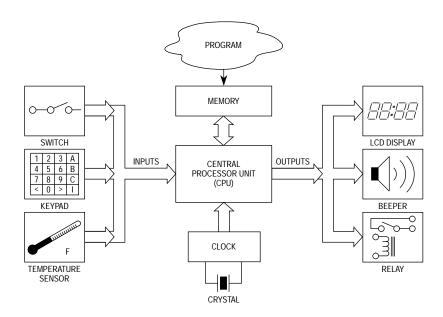

Whatever their size, all computer systems consist of the same fundamental parts: CPU, I/O devices, memory, program(s), and a timing reference (clock) as shown in **Figure 1**.

**Figure 1. A Typical Computer System**

The CPU processes information in accordance with a program of instructions and data in a particular language called machine code. The CPU controls all the system operations and provides control signals for enabling and disabling the various peripherals and I/O devices.

Input devices supply information to the MCU from the outside world. Some input devices convert analog signals into digital signals that the MCU can understand and manipulate. Other input devices translate real-world information into the 0 to + 5 Vdc signals required by MCUs. Examples of this are a temperature sensor, a switch, a keypad, and a typewriter-style keyboard. A computer system might have one or a number of these input devices.

Output devices are controlled by signals from the MCU. An external interface is required by some output devices to translate the 0 to + 5 Vdc MCU levels into different voltage or current levels. Liquid crystal displays, video display terminals, and heating/cooling equipment are examples of output devices.

Memory can store information, including the instructions and data that the CPU uses. The two basic memory types are random access memory (RAM and read-only memory (ROM).

RAM is used for temporary storage of data and instructions. The computer system can write information into and read information from a RAM in an arbitrary random order. RAM is volatile in that its contents are lost when power is removed.

ROM has data and instructions (a program) stored permanently in it when it is manufactured. The CPU can read information from a ROM but cannot write information into it. ROM information is nonvolatile in that it does not change even when power is removed.

A programmable read-only memory (PROM) is a type of ROM that can be programmed by the user.

An erasable programmable read-only memory (EPROM) is a type of PROM that can be erased by exposing it to ultraviolet light. Once erased, an EPROM may be reprogrammed with new instructions and data.

An OTPROM is a type of EPROM that is manufactured in an inexpensive plastic package. Since the plastic package is opaque to ultraviolet light, an OTPROM can be programmed only once.

Like ROM, PROM, EPROM, and OTPROM are nonvolatile types of memory.

The program contains instructions and data. The computer system uses the program to perform some desired processes.

The computer clock is used for timing and sequencing the various operations. A crystal is usually used to provide the reference frequency for the clock.

#### **Microcontroller Applications Overview**

The development of a new microcontroller application is limited only by skill and imagination, since the elements of a microcontroller system are easily assembled. MCU applications generally allow many new functions that make process control simpler and more powerful, often at reduced cost.

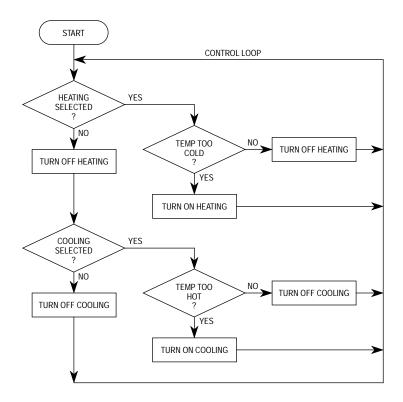

Many applications require analog inputs and outputs. The resulting system is the equivalent of a traditional analog controller with a number of control loops. Control loops regulate an output as a function of one or more inputs. Control loops are illustrated in the flowchart of **Figure 2**.

Figure 2. A Temperature Control Flowchart

Some applications have costly sensors and control mechanisms. The cost of the sensors required for input and the cost of the control devices required for output are usually much greater than the cost of a standard MCU.

The advantage of an MCU system is the use of software to replace complex and expensive hardware previously required. The cost of the software is a tradeoff against the cost of the additional hardware and the space it requires.

Programming allows use of complex functions that could not easily be accomplished with hard-wired devices. Changes in functions can be made and programs can be improved or replaced with few or no hardware changes.

#### **Project Description**

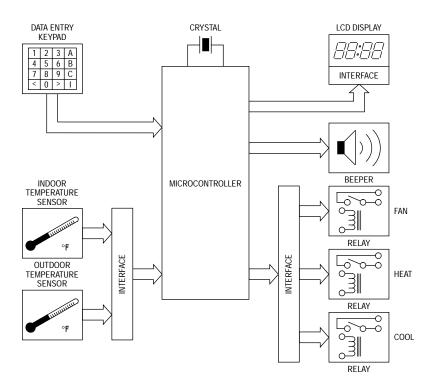

A basic thermostat controller was chosen for this project because it should be familiar to all readers and because it includes the fundamental elements common to all MCU applications. **Figure 3** illustrates a home thermostat controller that can control both heating and air conditioning.

Figure 3. Thermostat Project Block Diagram

Since the thermostat is based on an MCU, complex functions can be added. The thermostat could include a timed setback feature that allows specifying certain times of the day when there will be reduced demand for heating or air conditioning, thus giving some energy savings. A more unusual feature would be to measure the outdoor temperature and control the indoor-to-outdoor temperature difference. This would be very difficult to accomplish with a conventional electromechanical thermostat.

The four fundamental elements of this system are inputs, outputs, time, and a microcontroller to tie the other elements together. The inputs include push-buttons (a keypad) to enter time and temperature

M68HC05 Microcontroller Applications Guide — Rev. 3.0

information into the MCU and sensors to measure the indoor and outdoor temperatures. Outputs include a display to show system conditions and signals to the interfaces that control the heating and air conditioning equipment. Time is derived from a crystal connected to the MCU. As we will see later, this crystal would be used by the CPU even if the application did not have time-of-day requirements, A program controls the entire operation of the thermostat. **Applications** on page 197 of this manual contains project details.

# **Microcontroller Operation**

#### **Contents**

| Introduction                                 | 32 |

|----------------------------------------------|----|

| Number Systems                               | 34 |

| Computer Codes                               | 36 |

| Computer Memory                              | 39 |

| Computer Architecture                        | 39 |

| CPU Registers                                |    |

| Memory Uses                                  | 43 |

| Memory Maps                                  | 45 |

| Timing                                       | 47 |

| Programming                                  | 48 |

| Flowchart                                    |    |

| Mnemonic Source Code                         |    |

| Software Delay Program                       |    |

| Assembler Listing                            |    |

| CPU View of a Program                        |    |

| CPU Operation                                |    |

| Detailed Operation of CPU Instructions       | 60 |

| Store Accumulator (Direct Addressing Mode)   |    |

| Load Accumulator (Immediate Addressing Mode) |    |

| Conditional Branch                           |    |

| Subroutine Calls and Returns                 | 64 |

| Playing Computer                             | 67 |

| On-Chip Peripherals                          | 73 |

| Serial Communications Interface (SCI)        |    |

| Serial Peripheral Interface (SPI)            |    |

| 16-Bit Timer System                          |    |

| Memory Peripherals                           | 76 |

| Other On-Chip Peripherals                    |    |

#### Introduction

A microcontroller unit (MCU) is a complete computer system on a single silicon chip. In a great many controller applications, the MCU can satisfy all system requirements with no additional integrated circuits (ICs). Due to very low cost and a high degree of flexibility, these powerful new MCU devices are finding their way into many applications that were previously accomplished with combinational logic or even by mechanical means. As a result, there are many experienced engineers who need to become familiar with the function and application of Motorola MCUs. This section, which is specifically designed for those engineers, is also a good reference for engineers who are familiar with MCUs from some other manufacturer.

The MCU block in the thermostat block diagram of **Figure 3** on page 28 can be expanded as shown in **Figure 4** to show the functional blocks within the MCU. The CPU block is the central element of a digital binary computer much like mainframe computers used in business except that it is much smaller. The goal of this section is to study the internal operation of this CPU and how it interacts with the other functional blocks within the MCU. Although this discussion is based on a relatively simple CPU, the principles apply to even the most powerful mainframe computers.

The CPU is a system of simple logic elements and buses that can sequentially interpret and execute a finite set of instructions. Starting from a specific address in memory after reset, the CPU mindlessly fetches and executes one simple instruction after another. Each instruction is composed of several even simpler steps. The small substeps comprising each instruction are determined by the wiring within the CPU. The transistors, logic gates, and buses which comprise the CPU are called hardware. The instructions the CPU follows to accomplish an application task are determined by an end user or design engineer and are called a software program. Before we can get into the discussion of the internal operations of the CPU, some basic concepts must be understood. The following paragraphs discuss numbering systems and special codes used by computers.

Figure 4. MCU Expanded Block Diagram

#### **Number Systems**

Computers work best with information in a different form than people use. Humans typically work in the base 10 (decimal) numbering system (probably because we have ten fingers). Digital binary computers work in the base 2 (binary) numbering system because this allows all information to be represented by sets of digits, which can only be zeros or ones. In turn, a one or zero can be represented by the presence or absence of a logic voltage on a signal line or the on and off states of a simple switch.

In decimal (base 10) numbers, the weight of each digit is ten times as great as the digit immediately to its right. The rightmost digit of a decimal integer is the ones place, the digit to its left is the tens digit, and so on. In binary (base 2) numbers, the weight of each digit is two times as great as the digit immediately to its right. The rightmost digit of the binary integer is the ones digit, the next digit to the left is the twos digit, next is the fours digit, then the eights digit, and so on.

Although computers are quite comfortable working with binary numbers of 8, 16, or even 32 binary digits, humans find it very inconvenient to work with so many digits at a time. The base 16 (hexadecimal) numbering system offers a practical compromise. One hexadecimal digit can exactly represent four binary digits, thus, an 8-bit binary number can be expressed by two hexadecimal digits.

The correspondence between a hexadecimal digit and the four binary digits it represents is simple enough that humans who work with computers easily learn to mentally translate between the two. In hexadecimal (base 16) numbers, the weight of each digit is 16 times as great as the digit immediately to its right. The rightmost digit of a hexadecimal integer is the ones place, the digit to its left is the sixteens digit, and so on.

**Table 1** demonstrates the relationship between the decimal, binary, and hexadecimal representations of values. These three different numbering systems are just different ways to represent the same physical quantities.

Table 1. Decimal, Binary and Hexadecimal Equivalents

| Base 10 Decimal | Base 2 Binary       | Base 16<br>Hexadecimal |

|-----------------|---------------------|------------------------|

| 0               | 0000                | 0                      |

| 1               | 0001                | 1                      |

| 2               | 0010                | 2                      |

| 3               | 0011                | 3                      |

| 4               | 0100                | 4                      |

| 5               | 0101                | 5                      |

| 6               | 0110                | 6                      |

| 7               | 0111                | 7                      |

| 0               | 1000                | 8                      |

| 8 9             | 1001                | 9                      |

| 10              | 1010                | A                      |

| 10              | 1011                | В                      |

| 12              | 1100                | С                      |

| 13              | 1101                | D                      |

| 14              | 1110                | E                      |

| 15              | 1111                | F                      |

| 16              | 0001 0000           | 10                     |

| 17              | 0001 0001           | 11                     |

| 100             | 0110 0100           | 64                     |

| 255             | 1111 1111           | FF                     |

| 1024            | 0100 0000 0000      | 400                    |

| 65,535          | 1111 1111 1111 1111 | FFFF                   |

The letters A through F are used to represent the hexadecimal values corresponding to 10 through 15 because each hexadecimal digit can represent 16 different quantities; whereas, our customary numbers only include the 10 unique symbols (0 through 9). Thus, some other single-digit symbols had to be used to represent the hexadecimal values for 10 through 15.

To avoid confusion about whether a number is decimal or hexadecimal, hexadecimal numbers are preceded by the \$ symbol. For example, 64 means decimal "sixty-four"; whereas, \$64 means hexadecimal "six-four", which is equivalent to decimal 100. Some other computer manufacturers follow hexadecimal values with a capital H (as in 64H).

#### Microcontroller Operation

Hexadecimal is a good way to express and discuss numeric information processed by computers because it is easy for people to mentally convert between hexadecimal digits and their 4-bit binary equivalent. The hexadecimal notation is much more compact than binary while maintaining the binary connotations.

#### **Computer Codes**

Computers must handle many kinds of information other than just numbers. Text (alphanumeric characters) and instructions must be encoded in such a way that the computer can understand this information. The most common code for text information is the American Standard Code for Information Interchange (or ASCII). The ASCII code establishes a widely accepted correlation between alphanumeric characters and specific binary values. Using the ASCII code, \$41 corresponds to capital A, \$20 corresponds to a space character, etc. The ASCII code translates characters to 7-bit binary codes, but in practice the information is most often conveyed as 8-bit characters with the most significant bit equal to zero. This standard code allows equipment made by various manufacturers to communicate because all of the machines use this same code.

Computers use another code to give instructions to the CPU. This code is called an operation code or opcode. Each opcode instructs the CPU to execute a very specific sequence of steps that together accomplish an intended operation. Computers from different manufacturers use different sets of opcodes because these opcodes are internally hard-wired in the CPU logic. The instruction set for a specific CPU is the set of all opcodes that the CPU knows how to execute. Even though the opcodes differ from one computer to another, all digital binary computers perform the same kinds of basic tasks in similar ways. The CPU in the MC68HC05 MCU can understand 62 basic instructions. Some of these basic instructions have several slight variations, each requiring a separate opcode. The instruction set of the MC68HC05 includes 210 unique instruction opcodes. We will discuss how the CPU actually executes instructions a little later in this section after a few more basic concepts have been presented.

M68HC05 Microcontroller Applications Guide — Rev. 3.0

An opcode such as \$4C is understood by the CPU, but it is not very meaningful to a human. To solve this problem, a system of mnemonic instruction formats is used. The \$4C opcode corresponds to the INCA mnemonic, which is read "increment accumulator." Although there is printed information to show the correlation between mnemonic instructions and the opcodes they represent, this information is seldom used by a programmer because the translation process is automatically handled by a separate computer program called an assembler. An assembler is a program that converts a program written in mnemonics into a list of machine codes (opcodes) that can be used by a CPU.

An engineer develops a set of instructions for the computer in mnemonic form and then uses an assembler to translate these instructions into opcodes that the CPU can understand. We will discuss instructions, writing programs, and assemblers later in this applications guide, but you should understand that people prepare instructions for a computer in mnemonic form and the computer understands only opcodes; thus, a translation step is required to change the mnemonics to opcodes, and this is the function of the assembler.

Before leaving this discussion of number systems and codes, we will look at two additional codes you may have heard about. Octal (base 8) notation was used for some early computer work but is seldom used today. Octal notation uses the numbers 0 through 7 to represent sets of three binary digits in the same way hexadecimal is used to represent sets of four binary digits. The octal system had the advantage of using customary number symbols (unlike the hexadecimal symbols A through F discussed earlier).

Two disadvantages caused octal to be abandoned for the hexadecimal notation used today. First of all, most computers use 4, 8, 16, or 32 bits per word; these words do not break down nicely into sets of three bits. (Some early computers used 12-bit words which did break down into four sets of three bits each.) The second problem was that octal is not as compact as hexadecimal. For example, the ASCII value for capital A is 10000012 in binary, 4116 in hexadecimal, and 1018 in octal. When a human is talking about the ASCII value for A, it is easier to say "four-one" than it is to say "one-zero-one." When mentally translating from hexadecimal to binary, it is easy to convert each hexadecimal digit into

four binary bits. It is more difficult to make the octal-to-binary translation because you have to remember to throw away the leading zero of the first group of three binary bits. You probably had to think twice about that last statement, and that is exactly the point.

Binary coded decimal (BCD) is a hybrid notation used to express decimal values in binary form. BCD uses four binary bits to represent each decimal digit. Since four binary digits can express 16 different physical quantities there will be six bit-value combinations that are considered invalid (specifically, the hexadecimal values A through F). Values are kept in pseudo-decimal form during calculations.

When the computer does a BCD add operation, it performs a binary addition and then adjusts the result back to BCD form. As a simple example, consider the BCD addition of  $9_{10} + 1_{10} = 10_{10}$ . The computer adds  $0000\ 1001_2 + 0000\ 0001_2 = 0000\ 1010_2$ , but  $1010_2$  is equivalent to  $A_{16}$ , which is not a valid BCD value. When the computer finishes the calculation, a check is performed to see if the result is still a valid BCD value. If there was any carry from one BCD digit to another or if there was any invalid code, a sequence of steps would be performed to correct the result to proper BCD form  $(0000\ 1010_2)$  is corrected to  $0001\ 0000_2$  (BCD 10) in this example).

In most cases, it is inefficient to use BCD notation in computer calculations. It is better to change from decimal to binary as information is entered, do all computer calculations in binary, and change the binary result back to BCD or decimal as needed for display. First, not all computers are capable of doing BCD calculations because they need a digit-to-digit carry indicator which is not present on all computers (though Motorola MCUs do have this half-carry indicator). Secondly, forcing the computer to emulate human behavior is inherently less efficient than allowing the computer to work in its native binary system.

# **Computer Memory**

Before the operation of the CPU can be discussed in detail, some conceptual knowledge of computer memory is required. In many beginning programming classes, memory is presented as being similar to a matrix of pigeon holes where you can save messages and other information. The pigeon holes we are referring to are like the mailboxes in a large apartment building. This is a good analogy but needs a little refinement if it is to be used to explain the inner workings of a CPU. We will confine our discussion to an 8-bit CPU so that we can be very specific.

In an 8-bit CPU, each pigeon hole (or mailbox) can be thought of as containing a set of eight on/off switches (eight bits of data are called a byte of data). Unlike a pigeon hole, you cannot fit more information in by writing smaller, and there is no such thing as an empty pigeon hole (though the contents of a memory location can be unknown or undefined at a given time). The switches would be in a row where each switch would represent a single binary digit.

A binary one corresponds to the switch being on, and a binary zero corresponds to the switch being off. Each pigeon hole (memory location) has a unique address so that information can be stored and reliably retrieved.

#### Computer Architecture

Motorola M68HC05 and M68HC11 8-bit MCUs have a specific organization which is called a Von Neumann architecture after an American mathematician of the same name. In this architecture, a CPU and a memory array are interconnected by an address bus and a data bus. The address bus is used to identify which pigeon hole is being accessed, and the data bus is used to convey information either from the CPU to the memory location (pigeon hole) or from the memory location to the CPU.

In the Motorola implementation of this architecture, there are a few special pigeon holes (called CPU registers) inside the CPU, which act as a small scratch pad and control panel for the CPU. These CPU registers are similar to memory in that information can be written into them and

remembered. However, it is important to remember that these registers are directly wired into the CPU and are not part of the addressable memory available to the CPU.

All information (other than the CPU registers) accessible to the CPU is envisioned (by the CPU) to be in a single row of several thousand pigeon holes. This organization is sometimes called a 'memory-mapped I/O' system because the CPU treats all memory locations alike whether they contain program instructions, variable data, or input-output (I/O) controls. There are other computer architectures, but this applications guide is not intended to explore these variations. Fortunately, the Motorola architecture we are discussing is one of the easiest to understand and use. This architecture encompasses the most important concepts of digital binary computers; thus, the information presented in this applications guide will be applicable even if you go on to study other architectures.

The number of wires in the address bus determines the total possible number of pigeon holes; the number of wires in the data bus determines the amount of information that can be stored in each pigeon hole. In the MC68HC705C8, the address bus is 13 bits, making a maximum of 8192<sub>10</sub> separate pigeon holes (in MCU jargon you would say this CPU can access 8K locations). Since the data bus in the MC68HC705C8 is eight bits, each pigeon hole can hold one byte of information. One byte is eight binary digits, or two hexadecimal digits, or one ASCII character, or a decimal value from 0 to 255.

#### **CPU Registers**

Different CPUs have different sets of CPU registers. The differences are primarily the number and size of the registers. **Figure 5** shows the CPU registers found in an M68HC05. While this is a relatively simple set of CPU registers, it is representative of all types of CPU registers and can be used to explain all of the fundamental concepts.

Figure 5. M68HC05 CPU Registers

The A register, an 8-bit scratch-pad register, is also called an accumulator because it is often used to hold one of the operands or the result of an arithmetic operation.

The X register is an 8-bit index register, which can also serve as a simple scratch pad. The main purpose of an index register is to point at an area in memory where the CPU will load (read) or store (write) information. Sometimes an index register is called a pointer register. We will learn more about index registers when we discuss indexed addressing modes.

The program counter (PC) register is used by the CPU to keep track of the address of the next instruction to be executed. When the CPU is reset (starts up), the PC is loaded from a specific pair of memory locations called the reset vector. The reset vector locations contain the address of the first instruction to be executed by the CPU. As

instructions are executed, logic in the CPU increments the PC such that it always points to the next piece of information that the CPU will need. The number of bits in the PC exactly matches the number of wires in the address bus. This determines the total potentially available memory space that can be accessed by a CPU. In the case of an MC68HC705C8, the PC is 13 bits long; therefore, its CPU can access up to 8K bytes (8192) of memory. Values for this register are expressed as four hexadecimal digits where the upper-order three bits of the corresponding 16-bit binary address are always zero.

The condition code (CC) register is an 8-bit register holding status indicators that reflect the result of some prior CPU operation. The three high-order bits of this register are not used and always stay at logic one. Branch instructions use these status bits to make simple either or decisions.

The stack pointer (SP) is used as a pointer to the next available location in a last-in-first-out (LIFO) stack. The stack can be thought of as a pile of cards, each holding a single byte of information. At any given time, the CPU can put a card on top of the stack or take a card off the stack. Cards within the stack cannot be used unless all the cards piled on top are removed first. The CPU accomplishes this stack effect by way of the SP. The SP points to a memory location (pigeon hole), which is thought of as the next available card. When the CPU pushes a piece of data onto the stack, the data value is written into the pigeon hole pointed to by the SP; the SP is then decremented so it points at the next previous memory location (pigeon hole). When the CPU pulls a piece of data off the stack, the SP is incremented so it points at the most recently used pigeon hole, and the data value is read from that pigeon hole. When the CPU is first started up or after a reset stack pointer (RSP) instruction, the SP points to a specific memory location in RAM (a certain pigeon hole).

#### **Memory Uses**

The computer memory holds all information needed by the computer for instructions, variable data, and even I/O status and controls. Some memory locations contain fixed data like the instructions for the CPU and tables of constant data. This information is typically held in a read-only memory (ROM) although there is no special requirement that this information has to be located in ROM. A second type of information used by computers is variable information that changes often during the operation of the system. This type of data is typically held in a read-write random-access memory (RAM). Information can be read from or written to various locations in RAM in an arbitrary random order. A third type of information found in a computer system is I/O status and control information. This type of memory location allows the computer system to get information to or from the outside world. This type of memory location is unusual because the information can be sensed and, or changed by something other than the CPU.

The simplest kind of I/O memory locations are a simple input port and a simple output port. In an 8-bit MCU, a simple input port would consist of eight pins that can be read by the CPU. A simple output port would consist of eight pins that the CPU can control (write to). In practice, a simple output port location is usually implemented with eight latches and feedback paths that allow the CPU to read back what was previously written to the address of the output port.

**Figure 6** shows the equivalent circuit for one bit of RAM, one bit of an input port, and one bit of a typical output port having readback capability. In a real MCU, this circuit would be repeated eight times to make a single 8-bit RAM location, input port, or output port.

When the CPU stores a value to the address that corresponds to the RAM bit in **Figure 6** (a), the WRITE signal is activated to latch the data from the data bus line into the flip-flop [1]. This latch is static and remembers the value written until a new value is written to this location (or power is removed). When the CPU reads the address of this RAM bit, the READ signal is activated, which enables the multiplexer at [2]. This multiplexer couples the data from the output of the flip-flop into the data bus line. In a real MCU, RAM bits are actually much simpler than shown here, but they are functionally equivalent to this circuit.

When the CPU reads the address of the input port shown in **Figure 6** (b), the READ signal is activated, which enables the multiplexer at [3]. The multiplexer couples the buffered data from the pin onto the data bus line. A write to this address would have no meaning.

When the CPU stores a value to the address that corresponds to the output port in **Figure 6** (c), the WRITE signal is activated to latch the data from the data bus line into the flip-flop [4]. The output of this latch, which is buffered by the buffer driver at [5], appears as a digital level on the output pin. When the CPU reads the address of this output port, the READ signal is activated, which enables the multiplexer at [6). This multiplexer couples the data from the output of the flip-flop onto the data bus line.

Figure 6. Memory and I/O Circuitry

#### **Memory Maps**

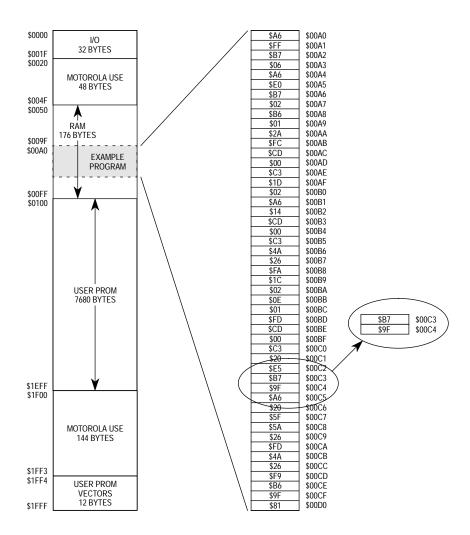

Since there are several thousand memory locations in the MCU system, it is important to have a convenient way to track locations. A memory map is a pictorial representation of the total MCU memory space. **Figure 7** is a typical memory map showing a subset of the memory resources in the MC68HC705C8. Some memory areas (reserved for Motorola use) were purposely left out of this figure to make it easier to understand. The complete version of this memory map can be found in the **Figure 22** on page 92.

Figure 7. Typical Memory Map

The four-digit hexadecimal values along the left edge of **Figure 7** are addresses beginning with \$0000 at the top and increasing to \$1FIFF at the bottom. \$0000 corresponds to the first memory location selected (when the CPU drives all address lines of the internal address bus to logic zero). \$1FFF corresponds to the last memory location selected (when the CPU drives all 13 address lines of the internal address bus to logic one). The labels within the vertical rectangle identify what kind of memory (RAM, PROM, I/O registers, etc.) resides in a particular area of memory.

Some areas, such as I/O registers, need to be shown in more detail because it is important to know the names of each individual location. The vertical rectangle can be interpreted as a row of 8192 pigeon holes (memory locations). Each of these 8192 memory locations contains eight bits of data as shown in the inset in **Figure 7**.

The first 256 memory locations (\$0000-\$00FF) can be accessed with the direct addressing mode of many CPU instructions. In this addressing mode, the CPU assumes that the upper two hexadecimal digits of address are always zeros; thus, only the two low-order digits of the address need to be explicitly given in the instruction. All on-chip I/O registers and 176 bytes of RAM are located in the \$0000-\$00FF area of memory. In the memory map (Figure 7), the expansion of the I/O area of memory identifies each register location with the two low-order digits of its address rather than the full four-digit address. For example, the two-digit hexadecimal value \$00 appears to the right of the port A data register, which is actually located at address \$0000 in the memory map.

Now that we have some background knowledge of computer memory, we can continue with our discussion of the CPU.

# **Timing**

A high-frequency clock source (typically derived from a crystal connected to the MCU) is used to control the sequencing of CPU instructions. Typical MCUs divide the basic crystal frequency by two or more to arrive at a bus-rate clock. Each memory read or write takes one bus-rate clock cycle. In the case of the MC68HC705C8 MCU, a 4-MHz (maximum) crystal oscillator clock is divided by two to arrive at a 2-MHz (maximum) internal processor clock. Each substep of an instruction takes one cycle of this internal processor clock (500 ns). Most instructions take two to five of these substeps; thus, the CPU is capable of executing about 500,000 instructions every second.

# **Programming**

At this point, we will write a short program in mnemonic form, translate it into machine code, and discuss how the CPU would execute the program. This exercise will provide insight into the internal operation of the CPU and computers in general. The instruction set explanations and the process of writing programs will be more understandable with this background.

Our program will read the state of a switch connected to an input pin. When the switch is closed, the program will cause an LED connected to an output pin to light for about one second and then go out. The LED will not light again until the switch has been released and closed again. The length of time the switch is held closed will not affect the length of time the LED is lighted.

Although this program is very simple, it demonstrates the most common elements of any MCU application program. First, it demonstrates how a program can sense input signals such as switch closures. Second, this is an example of a program controlling an output signal. Third, the LED on-time of about one second demonstrates one way a program can be used to measure real time. Because the algorithm is sufficiently complicated, it cannot be accomplished in a trivial manner with discrete components (at minimum, a one-shot IC with external timing components would be required). This example demonstrates that an MCU and a user-defined program (software) can replace complex circuits.

#### **Flowchart**

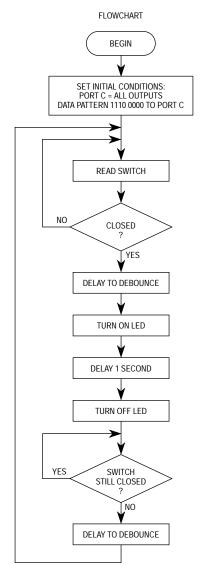

**Figure 8** is a flowchart of the example program. Flowcharts are often used as a planning tool for writing software programs because they show the function and flow of the program under development. The importance of notes, comments, and documentation for software cannot be overemphasized. Just as you would not consider a circuit-board design complete until there is a schematic diagram, parts list, and assembly drawing, you should not consider a program complete until there is a commented listing and a comprehensive explanation of the program such as a flowchart.

Figure 8. Example Flowchart

#### Mnemonic Source Code

Once the flowchart or plan is completed, the programmer develops a series of assembly language instructions to accomplish the functions called for in each block of the plan. The programmer is limited to selecting instructions from the instruction set for the CPU being used (in this case the MC68HC05).

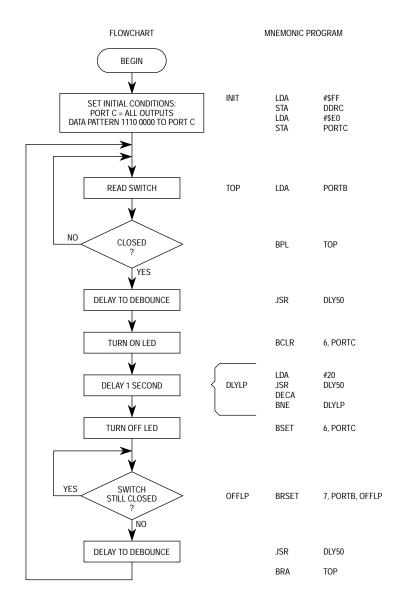

The programmer writes instructions in a mnemonic form which is easy to understand. **Figure 9** shows the mnemonic source code next to the flowchart of our example program so you can see what CPU instructions are used to accomplish each block of the flowchart. The meanings of the mnemonics used in the right side of **Figure 9** can be found in **Instruction Set Details** on page 245.

During development of the program instructions, it was noticed that a time delay was needed in three places. A subroutine was developed that would generate a 50-ms delay. This subroutine was used directly in two places (for switch debouncing) and made the one-second delay easier to produce. To keep this figure simple, the comments that would usually be included within the source program for documentation are omitted. The comments will be shown in the complete assembly listing in Figure 11.

Figure 9. Flowchart and Mnemonics

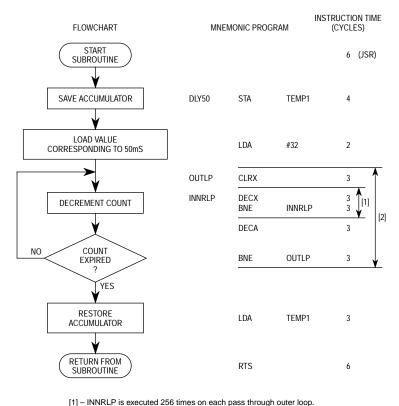

Software Delay Program Figure 10 shows an expanded flowchart of the 50-ms delay subroutine. A subroutine is a relatively small program which performs some commonly required function. Even if the function needs to be performed many times in the course of a program, the subroutine only has to be written once. Each place where this function is needed, the programmer would call the subroutine with a branch-to-subroutine (BSR) or jump-to-subroutine (JSR) instruction.

[1] – INNRLP is executed 256 times on each pass through outer loop.[2] – OUTLP is executed 32 times.

Figure 10. Delay Routine Flowchart and Mnemonics

Before starting to execute the instructions in the subroutine, the address of the instruction which follows the JSR (or BSR) is automatically stored in temporary RAM memory locations. When the CPU finishes executing the instructions within the subroutine, a return-from-subroutine (RTS) instruction is performed as the last instruction in the subroutine. The RTS instruction causes the CPU to recover the previously saved return address; thus, the CPU continues the program with the instruction following the JSR (or BSR) instruction that originally called the subroutine.

The delay routine of **Figure 10** involves an inner loop (INNRLP) within another loop (OUTLP). The inner loop consists of two instructions executed 256 times before X reaches \$00 and the BNE branch condition fails. This amounts to six cycles at 1  $\mu$ s/cycle times 256, which equals 1.536 ms for the inner loop. The outer loop executes 32 times. The total execution time for the outer loop is 32(1536+9) or 32(1545)=49.44 ms. The miscellaneous instructions in this routine other than those in the outer loop total 21 cycles; thus, the total time required to execute the DLY50 routine is 49.461 ms, including the time required for the JSR instruction that calls DLY50.

The 16-bit timer system in the MC68HC705C8 can also be used to measure time. The timer-based approach is actually preferred because the CPU can perform other tasks during the delay, and the delay time is not dependent on the exact number of instructions executed as it is in DLY50.

#### **Assembler Listing**

After a complete program or subprogram is written, it must be converted from mnemonics into binary machine code that the CPU can later execute. A separate computer system, such as an IBM PC, is used to perform this conversion to machine language. A computer program called an assembler is used. The assembler reads the mnemonic version of the program (also called the source version of the program) and produces a machine-code version of the program in a form that can be programmed into the memory of the MCU.

The assembler also produces a composite listing showing both the original source program (mnemonics) and the object code translation. This listing is used during the debug phase of a project and as part of the documentation for the software program. **Figure 11** shows the listing which results from assembling the example program. Comments were added before the program was assembled.

**Applications** on page 197 should be thoroughly studied before attempting to run any of the sample programs in this guide. Some of the sample programs were developed on another member of the M68HC05 Family which has a slightly different memory map than the MC68HC705C8. Minor modifications may be necessary to successfully run these programs on the MC68HC705C8.

Refer to **Figure 12** for the following discussion. This figure shows some lines of the listing with reference numbers indicating the various parts of the line. The first line is an example of an assembler directive line. This line is not really part of the program; rather, it provides information to the assembler so that the real program can be converted properly into binary machine code.

```

***************

* Simple 68HC05 Program Example

* Read sw connected to bit-7 of port B; 1 = closed

* When sw. closes, light LED for about 1 Sec; LED

* on when port C bit 6 = 0. wait for sw release,

* then repeat. Debounce sw 50ms on & off

**********

0001

Direct address of port B (sw)

PORTB

EQU

$01

0002

PORTC

EQU

$02

Direct address of port C (LED)

0005

Data direction control, port B

DDRB

EOU

$05

0006

DDRC

EQU

$06

Data direction control, port C

009f

TEMP1

EQU

$9F

One byte temp storage location

00a0

ORG

Program will start at $00A0

$A0

* $00A0 is in '705C8 RAM

00a0 a6 ff

INIT

LDA

#$FF

Begin initialization

00a2 b7 06

STA

Set port C to act as outputs

DDRC

* Port B is configured as inputs by default from reset.

00a4 a6 e0

Red & green LEDs and beeper off

LDA

#$E0

00a6 b7 02

STA

PORTC

Turn off red LED

* Some pins of port C (of my board) happen to be connected

* to devices which don't apply to this example program.

* The $EO pattern turns off my stuff & turns off red LED

00a8 b6 01

PORTB

Read sw at MSB of Port B

TOP

LDA

00aa 2a fc

BPL

TOP

Loop till MSB = 1 (Neg trick)

00ac cd 00 c3

Delay about 50 ms to debounce

JSR

DLY50

00af ld 02

BCLR

6,PORTC

Turn on LED (bit-6 to zero)

00bl a6 14

LDA

#20

Decimal 20 assembles to $14

00b3 cd 00 c3

Delay 50 ms

JSR

DLY50

DLYLP

00b6 4a

DECA

Loop counter for 20 loops

00b7 2 6 fa

BNE

DLYLP

20 times (20-19,19-18-1-0)

00b9 1c 02

Turn LED back off

BSET

6,PORTC

00bb Oe 01 fd

OFFLP

BRSET

7, PORTB, OFFLP Loop here till. sw off

00be cd 00 c3

Debounce release

JSR

DLY50

00cl 20 e5

Look for next sw closure

TOP

BRA

* * *

* DLY50-Subroutine to delay '-50ms

* Saves original accumulator value

* but X will always be zero on return

* * *

00c3 b7 9f

DLY50

STA

Save accumulator in RAM

TEMP1

00c5 a6 20

LDA

Do outer loop 32 times

00c7 5f

OUTLP

CLRX

X used as inner loop count

00c8 5a

INNRLP

DECX

O-FF, FF-FE,...1-0 256 loops

00c9 26 fd

6 \text{cyc} * 256 * 1 \mu \text{S/cyc} = 1.536 \text{ms}

BNE

INNRLP

00cb 4a

32-31, 31-30,...1-0

DECA

00cc 26 f9

1545 \text{cyc} * 32 * 1 \mu \text{S/cyc} = 49.440 \text{ms}

BNE

OUTLP

00ce b6 9f

LDA

TEMP1

Recover saved Accumulator val

00d0 81

** Return **

RTS

```

Figure 11. Assembler Listing

| 0001       | PORTB | EQU | \$01  | Direct address of port B (sw) |

|------------|-------|-----|-------|-------------------------------|

| 00a0       |       | ORG | \$A0  | Program will start at \$00A0  |

| 00a8 b6 01 | TOP   | LDA | PORTB | Read sw at MSB of Port B      |

|            |       |     |       |                               |

| [1] [2]    | [3]   | [4] | [5]   | [6]->                         |

Figure 12. Explanation of Assembler Listing

EQU, short for equate, is used to give a specific memory location or binary number a name which can then be used in other program instructions. In this case, the EQU directive is being used to assign the name PORTB to the value \$01, which is the address of port B in the MC68HC705C8. It is easier for a programmer to remember the mnemonic name PCRTB rather than the anonymous numeric value \$01. When the assembler encounters one of these names, the name is automatically converted to its corresponding binary value in much the same way that instruction mnemonics are converted into binary instruction codes.

The second line shown in **Figure 12** is another assembler directive. The mnemonic ORG, which is short for originate, tells the assembler where the program will start (the address of the start of the first instruction following the ORG directive line). ORG directives may be used more than once in a program to tell the assembler to put different parts of the program in specific places in memory. Refer to the memory map of the MCU to select an appropriate memory location where a program should start.

In this assembler listing, the first two fields, [1] and (2], are generated by the assembler, and the last four fields, [3], [4], [5], and [6], are the original source program written by the programmer. Field [3] is a label (TOP) which can be referred to in other instructions. In our example program, the last instruction was "BRA TOP", which simply means the CPU will continue execution with the instruction that is labeled "TOP".

When the programmer is writing a program, the addresses where instructions will be located are not typically known. Worse yet, in branch instructions, rather than using the address of a destination, the CPU uses an offset (difference) between the current PC value and the destination address. Fortunately, the programmer does not have to

worry about these problems because the assembler takes care of these details through a system of labels. This system of labels is a convenient way for the programmer to identify specific points in the program (without knowing their exact addresses); the assembler can later convert these mnemonic labels into specific memory addresses and even calculate offsets for branch instructions so that the CPU can use them.

Field [4] is the instruction field. The LDA mnemonic is short for load accumulator. Since there are six variations (different opcodes) of the load accumulator instruction, additional information is required before the assembler can choose the correct binary opcode for the CPU to use during execution of the program. Field [5] is the operand field, providing information about the specific memory location or value to be operated on by the instruction. The assembler uses both the instruction mnemonic and the operand specified in the source program to determine the specific opcode for the instruction.

The different ways of specifying the value to be operated on are called addressing modes (a more complete discussion of addressing modes is presented later). The syntax of the operand field is slightly different for each addressing mode so the assembler can determine the correct intended addressing mode from the syntax of the operand. In this case, the operand [5] is PORTB, which the assembler automatically converts to \$01 (recall the EQU directive). The assembler interprets \$01 as a direct addressing mode address between \$0000 and \$00FF, thus selecting the opcode \$136, which is the direct addressing mode variation of the LIDA instruction. If PCRTB had been preceded by a # symbol, that syntax would have been interpreted by the assembler as an immediate addressing mode value, and the opcode \$A6 would have been chosen instead of \$B6.

Field [6] is called the comment field and is not used by the assembler to translate the program into machine code. Rather, the comment field is used by the programmer to document the program. Although the CPU does not use this information during program execution, a good programmer knows that it is one of the most important parts of a good program. The comment [6] for this line of the program says "read sw at MSB of port B." This comment tells someone who is reading the listing why port B is being read, which is essential for understanding how the

program works. An entire line can be made into a comment line by using an asterisk (\*) as the first character in the line. In addition to good comments in the listing, it is also important to document programs with aflowchartorothercletailed information explaining the overall flow and operation of the program.

# CPU View of a Program

Figure 13, a memory map of the MC68HC705C8, shows how the example program fits in the memory of the MCU. This figure is the same as Figure 7 except that a different portion of the memory space has been expanded to show the contents of all locations in the program. Figure 13 shows that the CPU sees the example program as a linear sequence of binary codes, including instructions and operands in successive memory locations. The CPU begins this program with its program counter (PC) pointing at the first byte in the program. Each instruction opcode tells the CPU how many (if any) and what type of operands go with that instruction. In this way, the CPU can remain aligned to instruction boundaries even though the mixture of opcodes and operands looks confusing to us.